Una nueva investigación ha proporcionado otro medio más para robar datos confidenciales al explotar lo que es el primer canal lateral «en chip, entre núcleos» en los procesadores Intel Coffee Lake y Skylake.

Publicado por un grupo de académicos de la Universidad de Illinois en Urbana-Champaign, se espera que los hallazgos se presenten en el Simposio de Seguridad de USENIX que se celebrará en agosto.

Si bien se ha demostrado anteriormente que los ataques de fuga de información dirigidos a la microarquitectura de la CPU rompen el aislamiento entre las aplicaciones del usuario y el sistema operativo, permitiendo que un programa malicioso acceda a la memoria utilizada por otros programas (por ejemplo, Meltdown y Spectre), el nuevo ataque aprovecha una disputa sobre la interconexión del anillo.

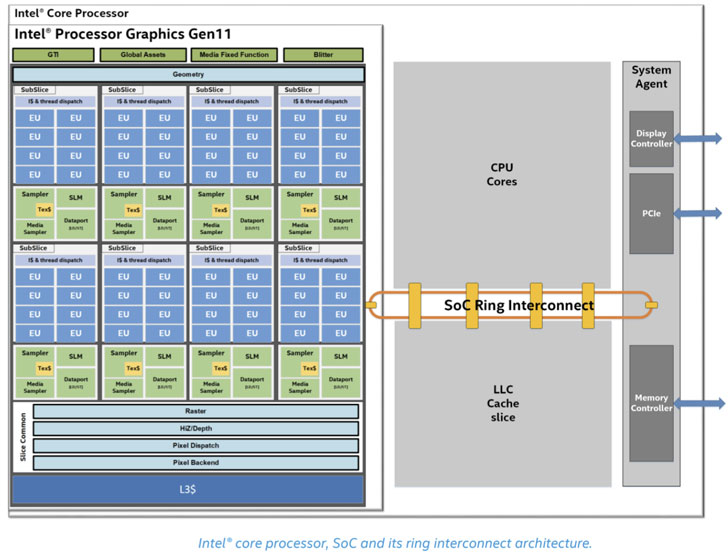

La interconexión de anillo de SoC es un bus integrado dispuesto en una topología de anillo que permite la comunicación dentro del proceso entre diferentes componentes (también conocidos como agentes) como los núcleos, la caché de último nivel (LLC), la unidad gráfica y el agente del sistema que son alojado dentro de la CPU. Cada agente de anillo se comunica con el anillo a través de lo que se llama una parada de llamada.

Para lograr esto, los investigadores realizaron ingeniería inversa de los protocolos de interconexión en anillo para descubrir las condiciones para que dos o más procesos causen una contención en el anillo, usándolos a su vez para construir un canal encubierto con una capacidad de 4.18 Mbps, que según los investigadores es más grande hasta la fecha para canales de núcleo cruzado que no dependen de la memoria compartida, a diferencia de Flush + Flush o Flush + Reload .

«Es importante destacar que, a diferencia de ataques anteriores, nuestros ataques no se basan en la memoria compartir, conjuntos de caché, los recursos básicos y privado o cualquier específicos Uncore estructuras», Riccardo Paccagnella, uno de los autores del estudio, dijo . «Como consecuencia, son difíciles de mitigar utilizando las técnicas de ‘aislamiento de dominio’ existentes».

Al observar que una parada de anillo siempre prioriza el tráfico que ya está en el anillo sobre el nuevo tráfico que ingresa de sus agentes, los investigadores dijeron que se produce una disputa cuando el tráfico existente en el anillo retrasa la inyección de nuevo tráfico de anillo.

Armado con esta información, un adversario puede medir el retraso en el acceso a la memoria asociado con un proceso malicioso debido a una saturación de la capacidad de ancho de banda causada por los accesos a la memoria de un proceso víctima. Sin embargo, esto requiere que el proceso de espionaje falte constantemente en sus cachés privados (L1-L2) y realice cargas desde un segmento de LLC de destino.

Al hacerlo, la latencia repetida en las cargas de memoria de LLC debido a la contención del anillo puede permitir que un atacante use las mediciones como un canal lateral para filtrar bits clave de implementaciones vulnerables de EdDSA y RSA, así como reconstruir contraseñas extrayendo la sincronización precisa. de pulsaciones de teclas escritas por un usuario víctima.

Específicamente, «un atacante con conocimiento de nuestros esfuerzos de ingeniería inversa puede configurarse de tal manera que sus cargas estén garantizadas para lidiar con las cargas del primer proceso, abusa […] de mitigaciones para programar ataques de caché de programación preventiva para causar que la víctima cargas que faltan en la caché, monitorea la contención del anillo mientras la víctima está computando y emplea un clasificador de aprendizaje automático estándar para eliminar el ruido y los bits de fuga «.

El estudio también marca la primera vez que se explota un canal de microarquitectura basado en contención para ataques de sincronización de pulsaciones de teclas para inferir datos confidenciales escritos por la víctima.

En respuesta a las divulgaciones, Intel clasificó los ataques como un «canal lateral tradicional», que se refiere a una clase de ataques de Oracle que normalmente aprovechan las diferencias en el tiempo de ejecución para inferir secretos.

Las pautas del fabricante de chips para contrarrestar los ataques de tiempo contra las implementaciones criptográficas recomiendan adherirse a los principios de programación de tiempo constante asegurándose de que:

- El tiempo de ejecución es independiente de los valores secretos

- El orden en el que se ejecutan las instrucciones (también conocido como patrones de acceso al código) es independiente de los valores secretos, y

- El orden en el que se cargan y almacenan los operandos de la memoria (patrones de acceso a datos) es independiente de los valores secretos